Preliminary – LD7701

Lighting Device Tech. Off-Line Voltage-mode PWM Generator

#### Features

- Wide input voltage range 9V~450V

- Internal 450V linear regulator (can be extended using external zener diodes)

亮芯科技股份有限公司

- Very low operating current <2mA</p>

- Internal 2% voltage reference

- 0% ~ 100% linear PWM signal

- Wide frequency range: 2KHz~13KHz

- Very few components for low cost solution

- +0.2A/-0.4A OUT drive

- Soft start

## Applications

- Battery powered LED lamps

- Table light with dimming control

#### **General Description**

LD7701 is a wide ranged input voltage PWM generator embedded with regulators. It needs very few external components to build a consumer product. Its PWN control can be full range controlled within 0%~100%. LD7701 can be applied on a low cost, limited space dimming control product.

For high power applications, the IC also comprises a 0.2A source and 0.4A sink OUT driver. There is an internal 9 to 450V linear regulator which powers the IC. This makes it no longer necessary to separate power supply for the IC.

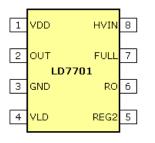

## Package Pin Out

## **Ordering Information**

|          |         | Packing Options |                 |  |

|----------|---------|-----------------|-----------------|--|

| Part No. | Package | Tube(TU)        | Tape & Reel(TR) |  |

| LD7701   | SOP-8   | LD7701S1-TU     | LD7701S1-TR     |  |

Package material default is "Green" package.

## **Product Marking**

Line 1 – "LD" is a fixed character 8888: product name

♦ Line 2 – SSSSS...: lot number

## **Absolute Maximum Ratings**

| Parameter                                             | Maximum      | Unit |  |  |  |

|-------------------------------------------------------|--------------|------|--|--|--|

| HVIN to GND                                           | -0.5~ +450   | V    |  |  |  |

| VDD to GND                                            | -0.3~ +13.5  | V    |  |  |  |

| OUT to GND                                            | -0.3~VDD+0.3 | V    |  |  |  |

| All other pins to GND                                 | -0.3~VDD+0.3 | V    |  |  |  |

| Continuous Power Dissipation ( $T_A = +25^{\circ}C$ ) |              |      |  |  |  |

| 8-Pin SOIC, de-rate 10.0mW/°C above +25°C             | 1000         | mW   |  |  |  |

| Junction to ambient thermal impedance                 | 82           | °C/W |  |  |  |

| Operating ambient temperature range                   | -40~ +85     | °C   |  |  |  |

| Junction temperature                                  | +125         | °C   |  |  |  |

| Storage temperature range                             | -65~ +150    | °C   |  |  |  |

The values beyond the boundaries of absolute maximum rating may cause the damage to the device. Functional operation in this context is not implied. Continuous use of the device at the absolute rating level might influence device reliability. All voltages have their reference to device ground.

## **Electrical Characteristics**

HVIN=24V, T<sub>A</sub>=25°C unless specified, otherwise minimum and maximum values are guaranteed by production testing requirements.

| Parameter                                     | Symbol                | Condition                                          | Min.            | Тур. | Max.  | Unit |

|-----------------------------------------------|-----------------------|----------------------------------------------------|-----------------|------|-------|------|

| Input                                         |                       |                                                    |                 |      |       |      |

| Input DC supply voltage range                 | HV <sub>IN</sub>      | DC input voltage                                   | 9 <sup>*1</sup> | -    | 450   | V    |

| Shut-down mode supply current                 | I <sub>INSD</sub>     | HVIN = 24V                                         | -               | 1.0  | 1.5   | mA   |

| Internal Regulator                            |                       |                                                    |                 |      |       |      |

| Internally regulated voltage                  | $V_{DD}$              | HVIN = 9~450V, IDD(ext) = 0                        | 7.25            | 7.75 | 8.25  | V    |

| External voltage applied on VDD <sup>*2</sup> | $V_{\text{DD(ext)}}$  | steady state external voltage                      | -               | -    | 12    | V    |

| Reference                                     |                       |                                                    |                 |      |       |      |

| REG2 pin voltage                              | $V_{\text{REG2}}$     | REG2 to GND with $0.1\mu$ F; VDD = 7.75V           | 1.225           | 1.25 | 1.275 | V    |

| Line regulation of REG2 voltage               | V <sub>REG2LINE</sub> | REG2 to GND with $0.1\mu$ F; VDD = $7.25 - 12V$    | 0               | -    | 20    | mV   |

| Load regulation of REG2 voltage               | $V_{\text{REG2LOAD}}$ | REG2 to GND with 0.1µF                             | 0               | -    | 20    | mV   |

| OUT                                           |                       |                                                    |                 |      |       |      |

| OUT short circuit current                     | ISOURCE               | V <sub>OUT</sub> = 0V; V <sub>DD</sub> = 7.75V     | 0.2             | -    | _     | А    |

| OUT sinking current                           | I <sub>SINK</sub>     | V <sub>OUT</sub> = 7.75V ; V <sub>DD</sub> = 7.75V | 0.4             | -    | _     | А    |

| OUT output rise time                          | T <sub>RISE</sub>     | C <sub>OUT</sub> = 1nF; V <sub>DD</sub> = 7.75V    | -               | 50   | 85    | ns   |

| OUT output fall time                          | T <sub>FALL</sub>     | C <sub>OUT</sub> = 1nF; V <sub>DD</sub> = 7.75V    | -               | 25   | 45    | ns   |

| Oscillator                                    |                       |                                                    |                 |      |       |      |

|                                               | f <sub>OSC1</sub>     | RO = 5MΩ                                           | 11.7            | 13   | 14.3  | KHz  |

| Oscillator frequency                          | f <sub>OSC2</sub>     | RO = 30MΩ                                          | 1.8             | 2    | 2.2   |      |

| Soft Start                                    |                       |                                                    |                 |      |       |      |

| Current into VLD pin when pulled low          | I <sub>VLD</sub>      | 6.25K $\Omega$ between REG2 and VLD                | _               | -    | 200   | μA   |

| FULL cut off voltage                          | V <sub>FULL</sub>     | OUT go high                                        | 5.5             | 6.0  | 6.5   | V    |

Notes: 1. See application section for minimum input voltage 2. Parameters are not guaranteed to be within specifications if the external VDD voltage is greater than VDD(ext) or if VDD < 7.25V.

| Pin Description |      |                                                                                                                             |  |  |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin #           | Name | Description                                                                                                                 |  |  |

| 1               | VDD  | This is a power supply pin for all internal circuits. It must be bypassed with a low ESR capacitor to GND (at least 0.1uF). |  |  |

| 2               | OUT  | This pin is the PWM output signal.                                                                                          |  |  |

| 3               | GND  | Ground return for all circuits. This pin must be connected to the return path from the input.                               |  |  |

| 4               | VLD  | This pin provides the adjustment of PWM pulse width.                                                                        |  |  |

| 5               | REG2 | This pin provides 2% accurate reference voltage. It must be bypassed with at least a 10nF - 0.22µF capacitor to GND.        |  |  |

| 6               | RO   | This pin sets the frequency by an external resistor between RO and GND.                                                     |  |  |

| 7               | FULL | This pin provides voltage to the comparator. When the voltage at this pin exceeds 6V, the OUT will be turned off.           |  |  |

| 8               | HVIN | This pin is the input of a 450V high voltage regulator.                                                                     |  |  |

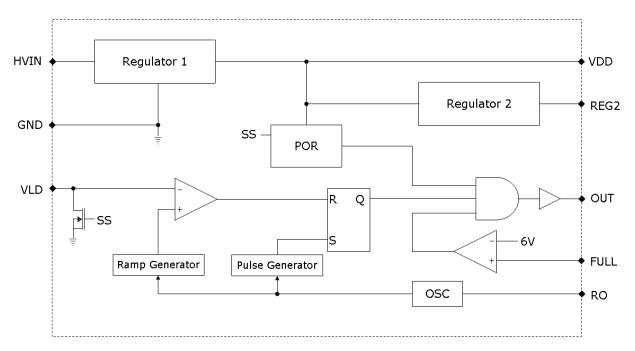

#### **Functional Block Diagram**

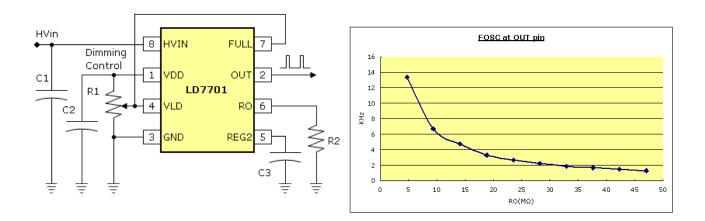

## **Typical Application Circuit**

# LD Tech Corporation

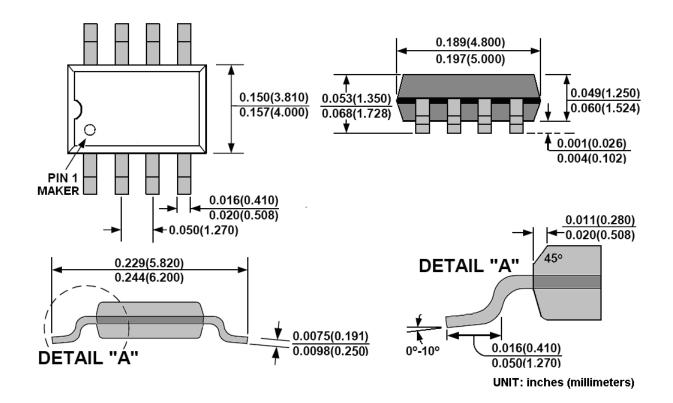

Package Outline

Tel:

+886-3-567-8806

Fax:

+886-3-567-8706

E-mail:

sales@ldtech.com.tw

Website:

www.ldtech.com.tw

Lighting Device Technologies Corporation DCC-LD7701-R1.0-20120102

Tel: +886-3-567-8806 Fax: +886-3-567-8706